Electrum-200 Manual/Hardware

From Manuals

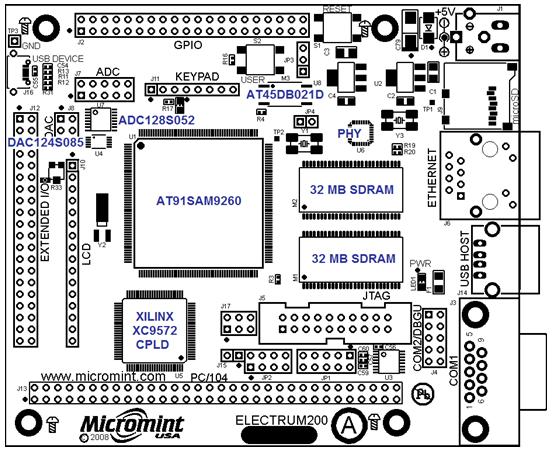

The following image shows where some of the hardware components are located.

Contents |

Microprocessor

The Electrum 200 includes an AT91SAM9260 microprocessor which is based on the integration of an ARM926EJ-S processor with fast ROM and RAM memories. This 32-bit ARM9 microprocessor is capable of 180-MHz operation. It has a wide range of peripherals including an Ethernet MAC, a USB Device Port, and a USB Host controller. Several standard peripherals are also included, such as USARTs, SPI bus, TWI bus (I2C), timers, and counters. Please see the Atmel Semiconductors ’ AT91SAM9260 Microprocessor Data Sheet for more information and register definitions.

AT91SAM9260 key features:

- Internal Memory

- 32 kilo-bytes internal ROM

- Two 4-kB internal SRAM

- Timers

- Two Three-channel 16-bit Timer/Counters

- Three External Clock Inputs, Two Multi-purpose I/O pins per channel

- Double PWM Generation, Capture/Waveform Mode, Up/Down Capability

- High-Drive Capability on Outputs TIOA0, TIOA1, TIOA2

- Periodic Interval Timer

- 20-bit interval Timer plus 12-bit Counter

- Watchdog Timer

- Key protected, Programmable Only Once

- Windowed 16-bit counter running on slow clock

- Real-time Timer

- 32-bit Free-running Backup Counter with 16-bit Prescaler

- Two Three-channel 16-bit Timer/Counters

- 10/100 Ethernet MAC

- 28-byte FIFOs

- Dedicated DMA Channels for Receive and Transmit

- Four Universal Synchronous/Asynchronous Receiver Transmitters (USART)

- Individual baud rate generator

- IrDA Infrared Modulation/Demodulation, Manchester Encoding

- Two Master/Slave Serial Peripheral Interface (SPI)

- 8-to 16-bit programmable data lengths

- Synchronous Communications

- One Two-wire Interface (TWI) (I2C)

- Master, multi-master or slave operation

- USB2.0 Full Speed (12 Mbits per second) Device Port

- On-chip transceiver

- 2,432-byte configurable DPRAM

- USB2.0 Full Speed (12 Mbits per second) Host Port

- Integrated FIFOs

- Dedicated DMA channels

- Three 32-bit Parallel Input/Output Controllers (PIOA, PIOB, PIOC)

- Input change interrupt on each I/O

- Individually programmable open-drain and pull-up resistor

- High current drive I/O lines, up to 16mA each

- Reset Controller

- Based on power-on reset cell

- Reset source identification

- Reset output control

- Additional Features

- IEEE 1149.1 JTAG Boundry Scan on all digital pins

- Programmable PLL for system clock

Data Flash

The Electrum 200 includes a 32k Byte Data Flash. The communication to the Data Flash is through a Serial Peripheral Interface bus (SPI). It has a maximum clock frequency of 66MHz. The Data Flash is used to store the boot-loader for the AT91SAM9260 microprocessor. For further information please see Atmel Semiconductors AT45DB021D Data Sheet.

SD RAM

The Electrum 200 includes positions for two 32MB SD RAMs for a total of 64MB. Read and write accesses to the SDRAM are burst oriented. Each access starts at a selected location and continue for a programmed number of locations. They have a self refresh mode and a 64mS, 8,192-cycle refresh. For further information please see Micron’s MT48LC16M16A2 Data Sheet.

NAND Flash

The Electrum 200 comes standard with a 1 GB NAND flash. The NAND Flash is capable of sequential reads in 25nS and can program a page in 220µS. An on-chip control logic automates program and erase operations to maximize cycle endurance. The program/erase endurance is specified at 100,000 cycles. For further information please see Micron Semiconductor’s MT29F4G08AAA Data Sheet.

PHY

The Electrum 200 includes Micrel KSZ8041NL 10 Base-T/100 Base-TX Physical Layer Transceiver (PHY). The PHY provides MII/RMII interface to transmit and receive data. It has HP Auto MDI/MDI-X to eliminate the need to differentiate between crossover and straight-through cables. For further information please see Micrel’s KSZ8041NL Data Sheet.

CPLD

A Xilinx’s XC9572XL Complex Programmable Logic Device(CPLD) comes standard with the Electrum 200. The CPLD supports in-system programming via an IEEE 1149.1 boundary-scan JTAG. The XC9572XL is a 3.3V CPLD with 5V tolerant pins. The CPLD has 1,600 usable gates and 72 macrocells. For further information please see Xilinx’s XC9500XL High-Performance CPLD Family Data Sheet.

DAC

A National Semiconductor’s DAC124S085 general purpose digital-to-analog converter (DAC) is an optional feature for the Electrum 200. The DAC has four channels with a resolution of 12-bit. The output amplifiers allow for a rail-to-rail output swing from 0 to 3.3V. Communication to the DAC is done through a three wire synchronous serial interface that operates up to 40 MHz. The DAC’s outputs have a settling time of 8.5µs. It allows for simultaneous output updating. For further information please see National Semiconductor’s DAC124S085 Data Sheet.

ADC

The Electrum 200 has an option to include a National Semiconductor’s ADC128S052 general purpose analog-to-digital converter (ADC). The ADC has eight channels with a resolution of 12-bit. The inputs can range from 0 to 3.3V. Communication to the ADC is done through a three wire synchronous serial interface that operates up to 8 MHz. The ADC’s inputs have a conversion rate up to 500 kSPS. For further information please see National Semiconductor’s ADC128S052 Data Sheet.