Bambino-200 Manual/Hardware

From Manuals

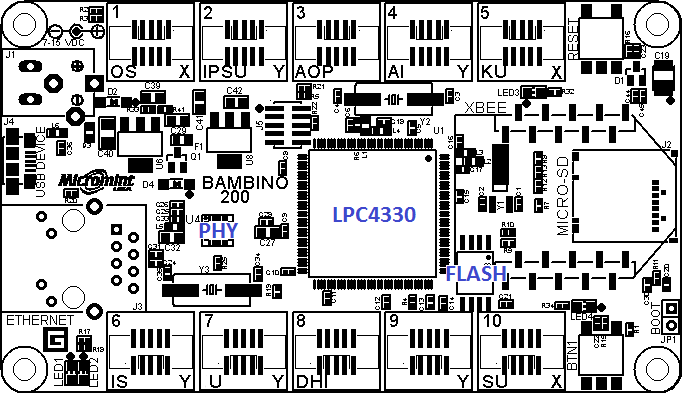

The following image shows where some of the hardware components are located.

Microcontroller

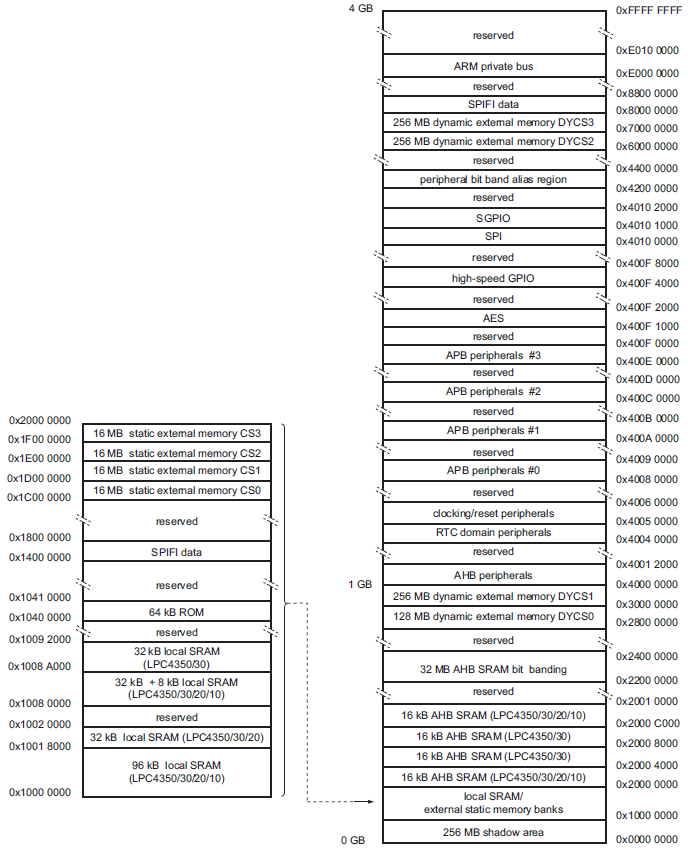

The Bambino 200 includes a NXP LPC4330 microcontroller. These dual core 32-bit ARM Cortex-M4/M0 RISC microcontroller are capable of 204-MHz operation with a Thumb2 instruction set for smaller object code. It uses a Harvard architecture with separate local instruction and data buses as well as a separate peripherals bus. Please see NXP’s LPC4330 Microcontroller's User Manual for more information and register definitions.

LPC4330 key features:

- Cortex-M4 Processor core

- Built-in Memory Protection Unit (MPU) supporting eight regions.

- Running at frequencies of up to 204 MHz.

- Built-in Nested Vectored Interrupt Controller (NVIC).

- Hardware floating-point unit.

- Non-maskable Interrupt (NMI) input.

- JTAG and Serial Wire Debug (SWD), serial trace, eight breakpoints, and four watch points.

- Enhanced Trace Module (ETM) and Enhanced Trace Buffer (ETB) support.

- System tick timer.

- Cortex-M0 Processor core

- Running at frequencies of up to 204 MHz.

- JTAG and built-in NVIC.