Bambino-200 Manual/Hardware

From Manuals

(Difference between revisions)

(Created page with '3 The following image shows where some of the hardware components are located. [[Image:Bambino-200-Hardware.png|center|alt=Bambino 200 Hardware D…') |

|||

| Line 11: | Line 11: | ||

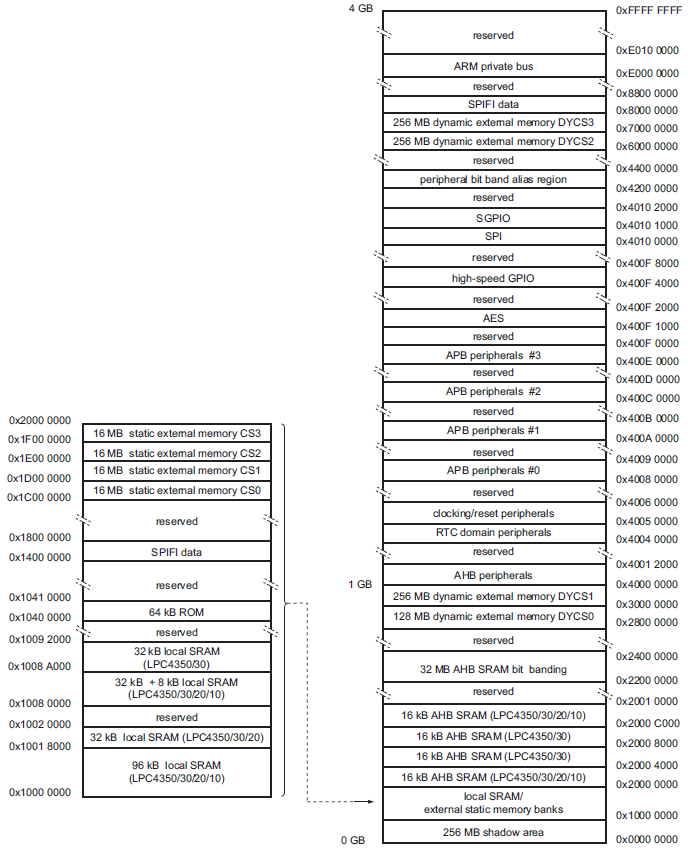

[[Image:Bambino-200-Mem-Map.png|center|alt=Bambino 200|frame|<div align="center">'''Bambino 200 Memory Map]] | [[Image:Bambino-200-Mem-Map.png|center|alt=Bambino 200|frame|<div align="center">'''Bambino 200 Memory Map]] | ||

</div> | </div> | ||

| - | |||

| - | |||

==Data Flash== | ==Data Flash== | ||

Revision as of 17:35, 31 May 2013

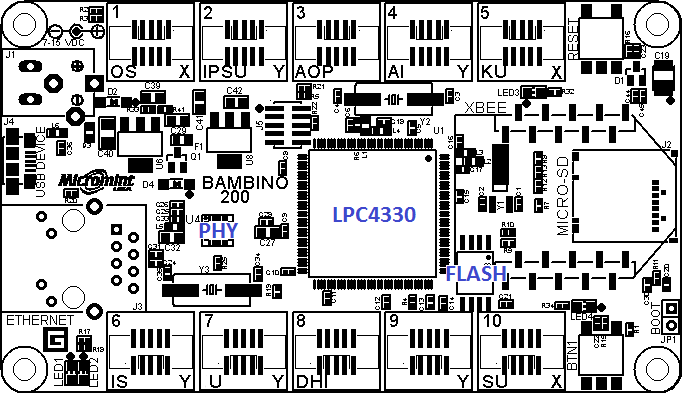

The following image shows where some of the hardware components are located.

Microcontroller

The Bambino 200 includes a NXP LPC4330 microcontroller. These dual core 32-bit ARM Cortex-M4/M0 RISC microcontroller are capable of 204-MHz operation with a Thumb2 instruction set for smaller object code. It uses a Harvard architecture with separate local instruction and data buses as well as a separate peripherals bus. Please see NXP’s LPC4330 Microcontroller's User Manual for more information and register definitions.

LPC4330 key features: