Bambino-200 Manual/Hardware

From Manuals

(Difference between revisions)

(→Microcontroller) |

(→Microcontroller) |

||

| Line 19: | Line 19: | ||

**Running at frequencies of up to 204 MHz. | **Running at frequencies of up to 204 MHz. | ||

**JTAG and built-in NVIC. | **JTAG and built-in NVIC. | ||

| + | *On-chip memory | ||

| + | ** 264 kB SRAM for code and data use. | ||

| + | **Multiple SRAM blocks with separate bus access. Two SRAM blocks can be powered down individually. | ||

| + | **64 kB ROM containing boot code and on-chip software drivers. | ||

| + | **128 bit general-purpose One-Time Programmable (OTP) memory. | ||

| + | *Clock generation unit | ||

| + | **Crystal oscillator with an operating range of 1 MHz to 25 MHz. | ||

| + | **12 MHz Internal RC (IRC) oscillator trimmed to 1 % accuracy over temperature and voltage. | ||

| + | **Ultra-low power Real-Time Clock (RTC) crystal oscillator. | ||

| + | **Three PLLs allow CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. The second PLL is dedicated to the High-speed USB, the third PLL can be used as audio PLL. | ||

| + | **Clock output. | ||

| + | *Configurable digital peripherals | ||

| + | **Serial GPIO (SGPIO) interface. | ||

| + | **State Configurable Timer (SCT) subsystem on AHB. | ||

| + | **Global Input Multiplexer Array (GIMA) allows to cross-connect multiple inputs and outputs to event driven peripherals like the timers, SCT, and ADC0/1. | ||

| + | *Serial interfaces | ||

| + | **Quad SPI Flash Interface (SPIFI) with 1-, 2-, or 4-bit data at rates of up to 52 MB per second. | ||

| + | **10/100T Ethernet MAC with RMII and MII interfaces and DMA support for high throughput at low CPU load. Support for IEEE 1588 time stamping/advanced time stamping (IEEE 1588-2008 v2). | ||

| + | **One High-speed USB 2.0 Host/Device/OTG interface with DMA support and on-chip high-speed PHY (USB0). | ||

| + | **One High-speed USB 2.0 Host/Device interface with DMA support, on-chip full-speed PHY and ULPI interface to external high-speed PHY (USB1). | ||

| + | **USB interface electrical test software included in ROM USB stack. | ||

| + | **Four 550 UARTs with DMA support: one UART with full modem interface; one UART with IrDA interface; three USARTs support UART synchronous mode and a smart card interface conforming to ISO7816 specification. | ||

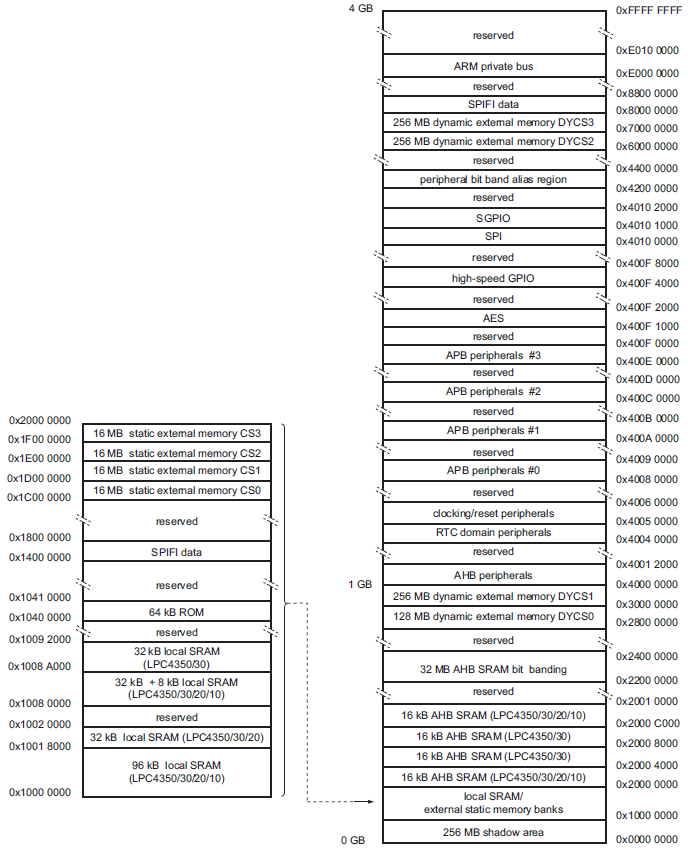

[[Image:Bambino-200-Mem-Map.png|center|alt=Bambino 200|frame|<div align="center">'''Bambino 200 Memory Map]] | [[Image:Bambino-200-Mem-Map.png|center|alt=Bambino 200|frame|<div align="center">'''Bambino 200 Memory Map]] | ||

Revision as of 17:55, 31 May 2013

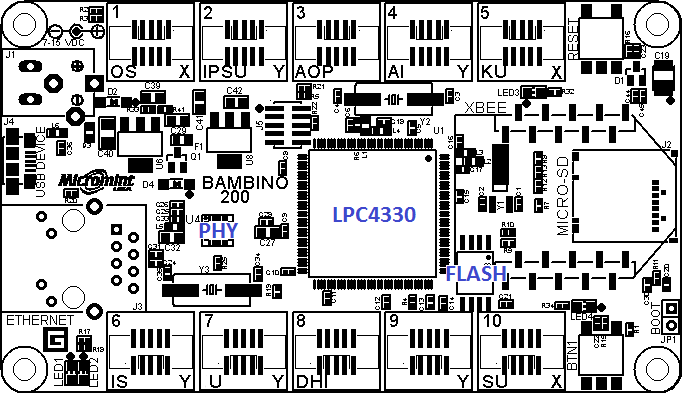

The following image shows where some of the hardware components are located.

Microcontroller

The Bambino 200 includes a NXP LPC4330 microcontroller. These dual core 32-bit ARM Cortex-M4/M0 RISC microcontroller are capable of 204-MHz operation with a Thumb2 instruction set for smaller object code. It uses a Harvard architecture with separate local instruction and data buses as well as a separate peripherals bus. Please see NXP’s LPC4330 Microcontroller's User Manual for more information and register definitions.

LPC4330 key features:

- Cortex-M4 Processor core

- Built-in Memory Protection Unit (MPU) supporting eight regions.

- Running at frequencies of up to 204 MHz.

- Built-in Nested Vectored Interrupt Controller (NVIC).

- Hardware floating-point unit.

- Non-maskable Interrupt (NMI) input.

- JTAG and Serial Wire Debug (SWD), serial trace, eight breakpoints, and four watch points.

- Enhanced Trace Module (ETM) and Enhanced Trace Buffer (ETB) support.

- System tick timer.

- Cortex-M0 Processor core

- Running at frequencies of up to 204 MHz.

- JTAG and built-in NVIC.

- On-chip memory

- 264 kB SRAM for code and data use.

- Multiple SRAM blocks with separate bus access. Two SRAM blocks can be powered down individually.

- 64 kB ROM containing boot code and on-chip software drivers.

- 128 bit general-purpose One-Time Programmable (OTP) memory.

- Clock generation unit

- Crystal oscillator with an operating range of 1 MHz to 25 MHz.

- 12 MHz Internal RC (IRC) oscillator trimmed to 1 % accuracy over temperature and voltage.

- Ultra-low power Real-Time Clock (RTC) crystal oscillator.

- Three PLLs allow CPU operation up to the maximum CPU rate without the need for a high-frequency crystal. The second PLL is dedicated to the High-speed USB, the third PLL can be used as audio PLL.

- Clock output.

- Configurable digital peripherals

- Serial GPIO (SGPIO) interface.

- State Configurable Timer (SCT) subsystem on AHB.

- Global Input Multiplexer Array (GIMA) allows to cross-connect multiple inputs and outputs to event driven peripherals like the timers, SCT, and ADC0/1.

- Serial interfaces

- Quad SPI Flash Interface (SPIFI) with 1-, 2-, or 4-bit data at rates of up to 52 MB per second.

- 10/100T Ethernet MAC with RMII and MII interfaces and DMA support for high throughput at low CPU load. Support for IEEE 1588 time stamping/advanced time stamping (IEEE 1588-2008 v2).

- One High-speed USB 2.0 Host/Device/OTG interface with DMA support and on-chip high-speed PHY (USB0).

- One High-speed USB 2.0 Host/Device interface with DMA support, on-chip full-speed PHY and ULPI interface to external high-speed PHY (USB1).

- USB interface electrical test software included in ROM USB stack.

- Four 550 UARTs with DMA support: one UART with full modem interface; one UART with IrDA interface; three USARTs support UART synchronous mode and a smart card interface conforming to ISO7816 specification.